关键词:deassign,force,release

过程连续赋值是过程赋值的一种。这种赋值语句能够替换其他所有 wire 或 reg 的赋值,改写了 wire 或 reg 型变量的当前值。

与过程赋值不同的是,过程连续赋值的表达式能被连续的驱动到 wire 或 reg 型变量中,即过程连续赋值发生作用时,右端表达式中任意操作数的变化都会引起过程连续赋值语句的重新执行。

过程连续性赋值主要有 2 种,assign-deassign 和 force-release。

assign, deassign

assign(过程赋值操作)与 deassign (取消过程赋值操作)表示第一类过程连续赋值语句。赋值对象只能是寄存器或寄存器组,而不能是 wire 型变量。

赋值过程中对寄存器连续赋值,寄存器中的值被保留直到被重新赋值。

例如,一个带复位端的 D 触发器可以用下面代码描述:

实例

input rstn,

input clk,

input D,

output reg Q

);

always @(posedge clk or negedge rstn) begin

if(!rstn) begin //Q = 0 after reset effective

Q <= 1'b0 ;

end

else begin

Q <= D ; //Q = D at posedge of clock

end

end

endmodule

下面,用 assign 与 deassign 改写,完成相同的功能。

即在复位信号为 0 时,Q 端被 assign 语句赋值,始终输出为 0。

复位信号为 1 时,Q 端被 deassign 语句取消赋值,在时钟上升沿被重新赋值。

实例

input rstn,

input clk,

input D,

output reg Q

);

always @(posedge clk) begin

Q <= D ; //Q = D at posedge of clock

end

always @(negedge rstn) begin

if(!rstn) begin

assign Q = 1'b0 ; //change Q value when reset effective

end

else begin //cancel the Q value overlay,

deassign Q ; //and Q remains 0-value until the coming of clock posedge

end

end

endmodule

force, release

force (强制赋值操作)与 release(取消强制赋值)表示第二类过程连续赋值语句。

使用方法和效果,和 assign 与 deassign 类似,但赋值对象可以是 reg 型变量,也可以是 wire 型变量。

因为是无条件强制赋值,一般多用于交互式调试过程,不要在设计模块中使用。

当 force 作用在寄存器上时,寄存器当前值被覆盖;release 时该寄存器值将继续保留强制赋值时的值。之后,该寄存器的值可以被原有的过程赋值语句改变。

当 force 作用在线网上时,线网值也会被强制赋值。但是,一旦 release 该线网型变量,其值马上变为原有的驱动值。

为直观的观察两种类型变量强制赋值的区别,利用第一节中的计数器 counter10 作为设计模块,testbench 设计如下。

实例

module test ;

reg rstn ;

reg clk ;

reg [3:0] cnt ;

wire cout ;

counter10 u_counter (

.rstn (rstn),

.clk (clk),

.cnt (cnt),

.cout (cout));

initial begin

clk = 0 ;

rstn = 0 ;

#10 ;

rstn = 1'b1 ;

wait (test.u_counter.cnt_temp == 4'd4) ;

@(negedge clk) ;

force test.u_counter.cnt_temp = 4'd6 ;

force test.u_counter.cout = 1'b1 ;

#40 ;

@(negedge clk) ;

release test.u_counter.cnt_temp ;

release test.u_counter.cout ;

end

initial begin

clk = 0 ;

forever #10 clk = ~ clk ;

end

//finish the simulation

always begin

#1000;

if ($time >= 1000) $finish ;

end

endmodule // test

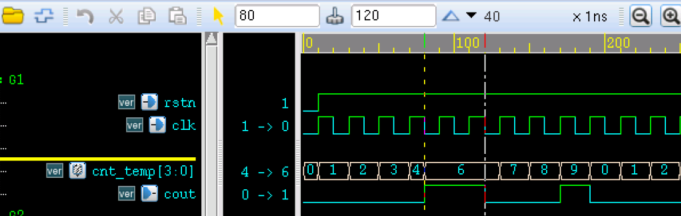

仿真结果如下。

由图可知,在 cnt_temp 等于 4 时(80ns), cnt_temp 被强制赋值为 6,cout 被强制赋值为 1。

release 时(120ns), cnt_temp 为寄存器类型,仍然保持原有值不变,直到时钟上升沿对其进行加法赋值操作,值才变为 7 。

而 120ns 时,由于 cout 是线网型变量,其值不能保存。原码 counter10 模型中存在驱动语句: assign cout = (cnt_temp==4'd9) ,所以 cout 值变为 0 。

点我分享笔记